```

demo-ret.ys

Return Example

0x000:

irmovq Stack,%rsp # Intialize stack pointer

# Avoid hazard on %rsp

nop

0x00b:

0x00c:

nop

call p

# Procedure call

irmovq $5,%rsi

0*016

# Return point

0x020:

halt

0x020: .pos 0x20

0x020: p: nop

# procedure

0x021:

nop

0x022:

nop

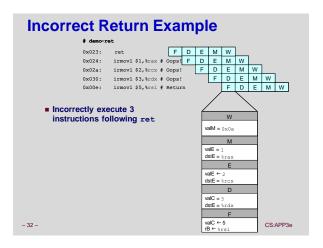

0x023:

ret

0x024:

irmovq $1,%rax

# Should not be executed

0x02e: irmovq $2,%rcx

0x038: irmovq $3,%rdx

0x042: irmovq $4,%rbx

# Should not be executed

# Should not be executed

# Should not be executed

0x100: .pos 0x100

# Initial stack pointer

0x100: Stack:

■ Require lots of nops to avoid data hazards

```

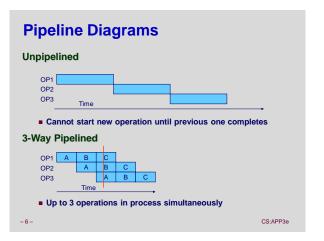

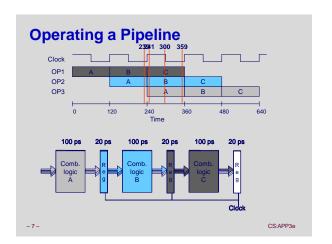

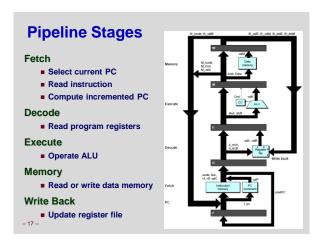

# **Pipeline Summary**

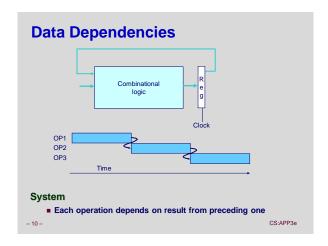

#### Concept

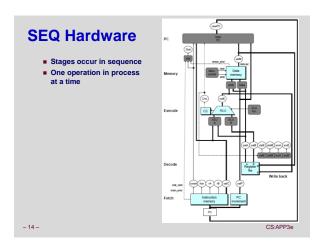

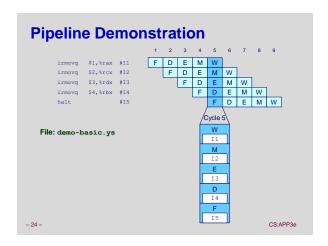

- Break instruction execution into 5 stages

- Run instructions through in pipelined mode

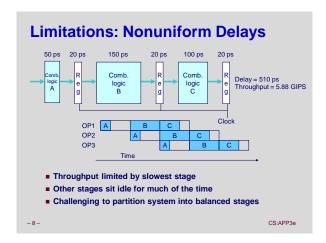

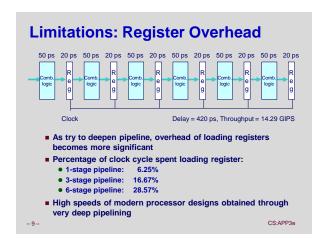

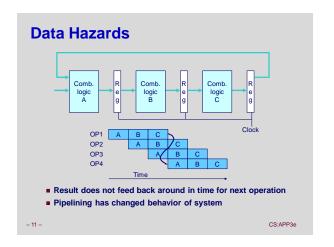

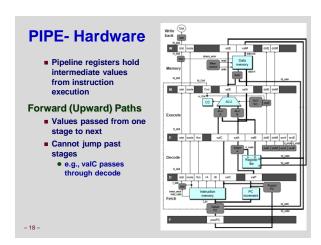

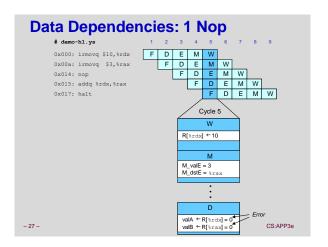

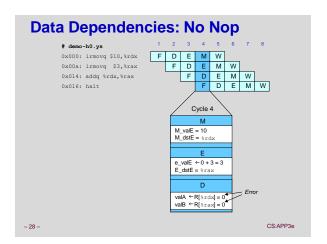

#### Limitations

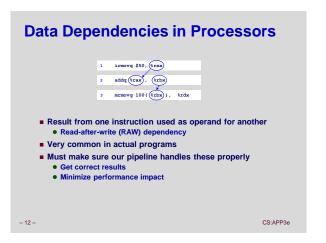

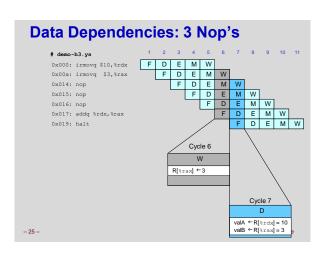

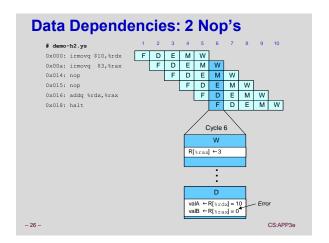

- Can't handle dependencies between instructions when instructions follow too closely

- Data dependencies

- One instruction writes register, later one reads it

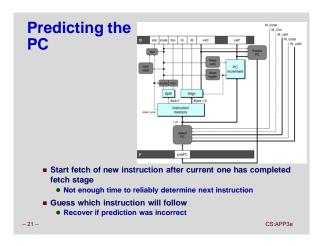

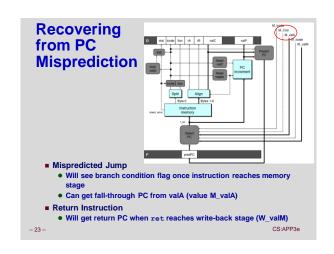

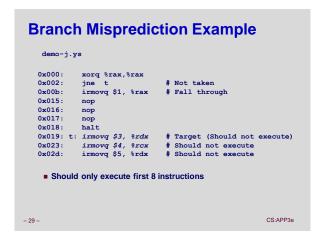

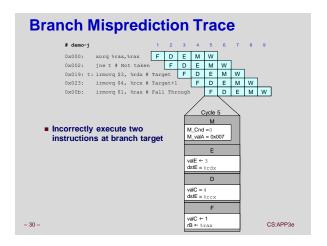

- Control dependency

- Instruction sets PC in way that pipeline did not predict correctly

- Mispredicted branch and return

### Fixing the Pipeline

■ Textbook gives more details of fixing techniques

- 34 – CS:APP3e

## **Fixing the Pipeline**

- · Stalling: make later stages wait until data is available

- · Insert fake instructions called "bubbles" in pipeline

- · Always possible, but can waste a lot of time

- · Used for PC after ret, and data loads

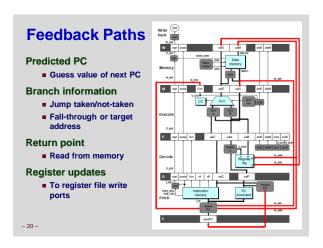

- Forwarding: add extra wires to make data available sooner

- E.g., "bypass path" from e\_valE to d\_valA bypassing register file

- · Requires more complex control logic

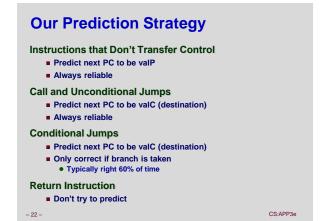

- · Branch prediction

- · Guess (e.g.) that branches will always be taken

- If guess is wrong, mis-predicted instructions turn into bubbles

CS:APP3e